Latch up in VLSI

In VLSI (Very Large Scale Integration) design, a latch-up refers to a phenomenon in which an integrated circuit becomes self-sustaining in a high-current state, leading to a functional failure of the device.A latch-up can occur in a CMOS (Complementary Metal Oxide Semiconductor) device when a parasitic thyristor is inadvertently created due to the layout or design of the circuit.

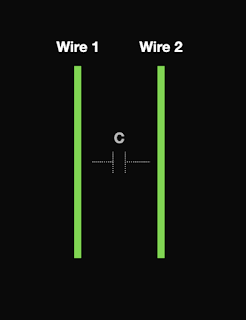

Visualise Latch up :

The parasitic thyristor is a structure that consists of two transistors (PNP and NPN) connected in a positive feedback loop. If the voltage at one of the nodes rises above a certain threshold, it can trigger the parasitic thyristor, causing it to conduct a large amount of current, which can damage or destroy the circuit.The latch-up condition can be triggered by various factors, such as a power supply glitch, electromagnetic interference, or even a high-temperature environment. The effect of latch-up is often permanent and can only be resolved by either powering off the device or physically removing the source of the problem.

How to avoid latch up ?

Designers can take measures to prevent latch-up in VLSI circuits, such as using layout rules that minimize the formation of parasitic structures, placing guard rings around sensitive areas, and adding circuitry to detect and prevent latch-up. By carefully considering the layout and design of the circuit, the risk of latch-up can be greatly reduced.